この章では、複数の信号から所望の要素を抽出するセレクタ(マルチプレクサ)というパーツを設計し、前章で作った計算機に新しい機能を追加します。

セレクタは 3 つの入力端子 \(S, X, Y\) をもち、1 つの出力端子 \(Z\) をもちます。セレクタの役割は \(X\) か \(Y\) の信号のどちらかを選ぶというものです。\(S = 0\) であれば \(X\) を出力し、\(S = 1\) であれば \(Y\) を出力します。真理値表は以下のようになります。

| S | X | Y | Z |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

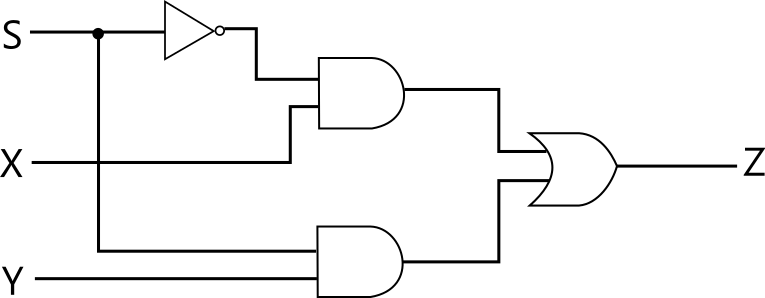

セレクタを AND, OR, NOT 素子を使って設計しましょう。ここで重要な役割を果たすのは AND 素子です。(NOT S) AND X の値は、\(S = 1\) であれば \(X\) に値にかかわらず常に \(0\) となり、\(S = 0\) であれば \(X\) と同じ値になります。S AND Y の値は、\(S = 0\) であれば \(Y\) の値にかかわらず常に \(0\) となり、\(S = 1\) であれば \(Y\) と同じ値になります。これらを OR 演算で組み合わせるとまさしくセレクタになります。よって、セレクタは以下のような回路で表されます。

実際にいくつかの入力パターンを試して真理値表と一致することを確かめてみてください。

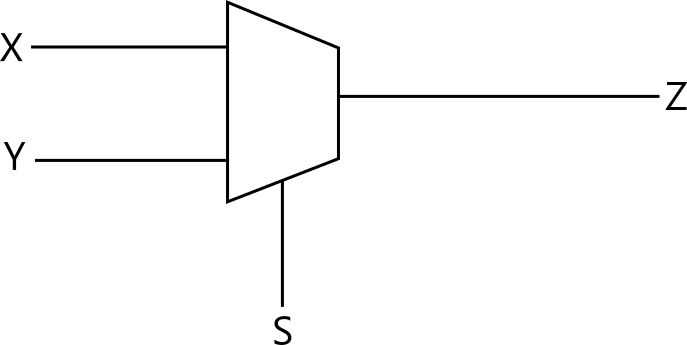

パーツを作ったので抽象化しておきましょう。セレクタは台形で表すことにします。制御信号は台形の側面に接続して描くことが多いのでここでもその慣例に従います。

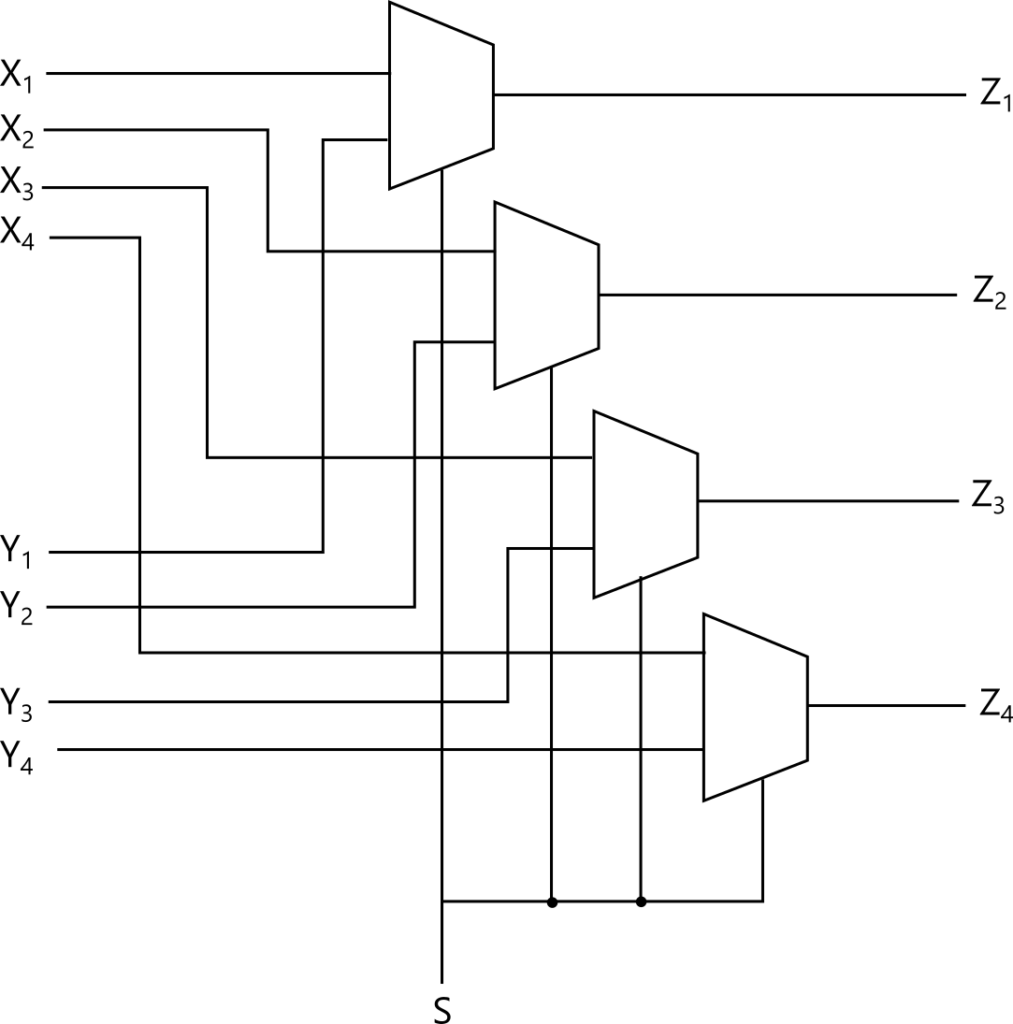

セレクタは複数桁の入力と組み合わせたときに力を発揮します。上で設計したセレクタを並べてみましょう。ただし、制御信号 S の部分には全てに同じ信号を入力します。4 ビットの場合では、図にすると以下のようになります。

この回路の入力は 9 つ \(S, X_1, X_2, X_3, X_4, Y_1, Y_2, Y_3, Y_4\), 出力は 4 つ \(Z_1, Z_2, Z_3, Z_4\) です。セレクタの各桁の \(S\) の部分は共通する信号が入っているので、\(S = 0\) のとき出力は \(X_1, X_2, X_3, X_4\) となり、\(S = 1\) のとき出力は \(Y_1, Y_2, Y_3, Y_4\) となります。つまり、\(S\) によって複数桁の入力を一気に選択することができます。

複数桁のセレクタも同様に台形で表すことにします。

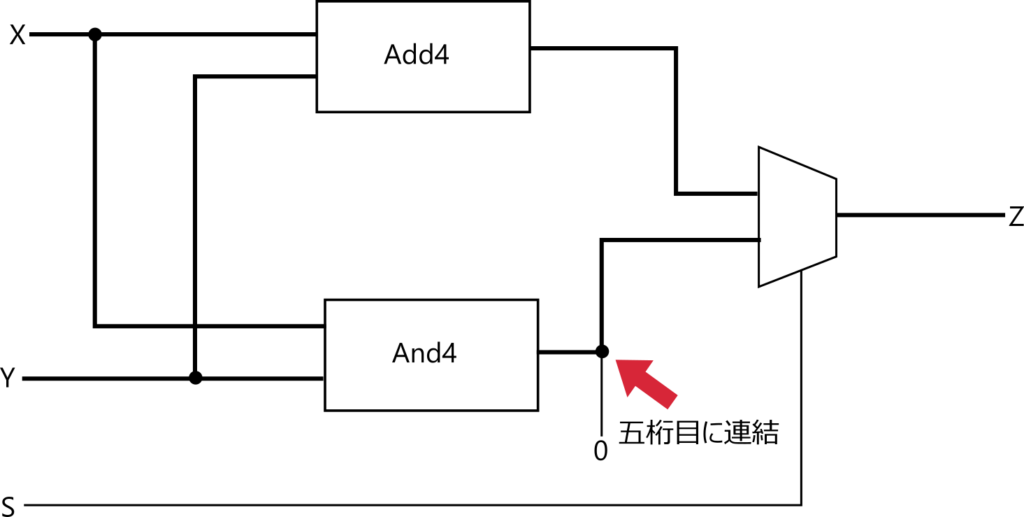

マセレクタにより、計算機に複数の機能を追加することができます。例として AND 演算を取りましょう。複数桁の AND 演算器を ANDn と書いた四角であわらすことにします。

新しく機能が増えた計算器では、入力を 9 つ, \(S, X_1, X_2, X_3, X_4, Y_1, Y_2, Y_3, Y_4\) を取り、出力が 5 つ \(Z_1, Z_2, Z_3, Z_4, Z_5\) としましょう。\(X_1, X_2, X_3, X_4\) を二進数として解釈した数を \(X\) とし、\(Y, Z\) も同様に定義します。

新しい計算機は \(S = 0\) のとき \(Z = X + Y\) とし、\(S = 1\) のとき Z = X AND Y (ビット毎論理積) を出力することにします。

設計の方針は、とりあえず \(X と Y\) を加算器と AND 演算器の両方に入力してしまい、後からセレクタで結果を選択するようにしましょう。AND の出力は 4 桁なので 5 桁目は 0 に固定してしまいます。回路図は以下のようになります。

このように、どちらの演算器に入れるかを前もって決めるのではなく、とりあえず両方に入れてしまって、後からどちらの結果を使うかを決めるという方法はよく使われます。

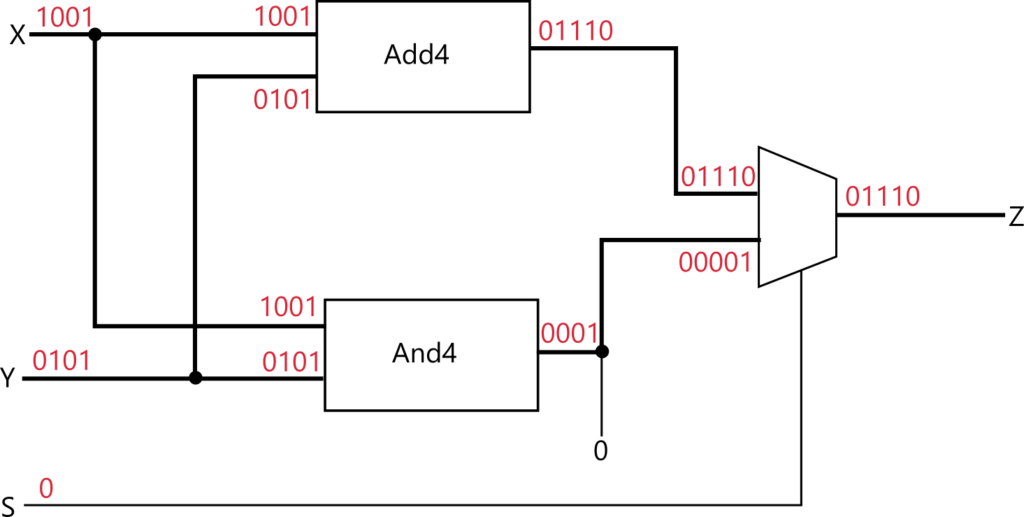

これでうまく動作しているか確認しましょう。例えば、\(S = 0, X = 1001, Y = 0101\) とすると、セレクタで加算器側から入ってきた信号が選択され、出力は \(Z = 01101\) となります。

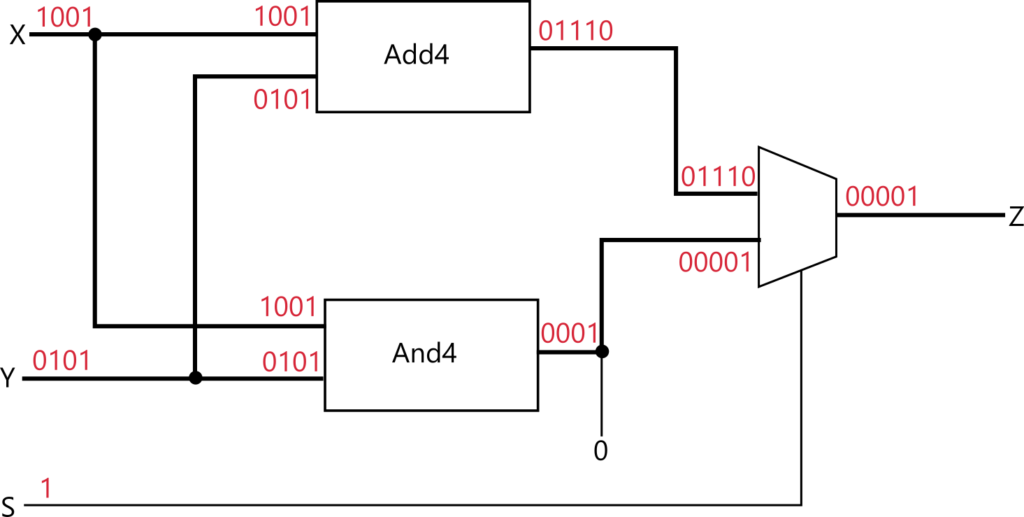

ここで \(S\) だけスイッチを切り替えて \(S = 1, X = 1001, Y = 0101\) とすると、AND 演算器側の結果が選択されるようになり、出力は \(Z = 00001\) となります。

このように、一つの回路の中で、どのような計算をするかをセレクタにより制御できます。

- セレクタは制御信号と 2 つの信号を受け取り、制御信号によってどちらか一方の信号を出力する

- 複数桁のセレクタは 1 bit マルチプレクサを並列に並べて制御信号を共通化することで実装できる

- マルチプレクサにより計算結果の制御が行える

これまでは入力に応じて直ちに出力が決まる回路のみを考えてきましたが、次章以降は記憶状態をもつ回路を考えていきます。